ДОНСКОЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ УПРАВЛЕНИЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ И ПОВЫШЕНИЯ КВАЛИФИКАЦИИ

Кафедра «Информационные системы в строительстве»

# Сборник задач

к проведению лабораторных занятий по дисциплине

# «Схемотехническое проектирование средств ВТ»

Автор Кокарева Я.А.

# **Аннотация**

Методические указания предназначены для студентов, обучающихся по направлению 09.03.01 «Информатика и вычислительная техника», профиль подготовки – «Системы автоматизированного проектирования»

# **Автор**

к.т.н., доцент кафедры «ИСС» Кокарева Я.А.

# Оглавление

| ВВЕДЕНИЕ        |          |            |                   | 4  |

|-----------------|----------|------------|-------------------|----|

| Лабораторная ра | бота №1. | Дешифр     | аторы и шифраторы | 5  |

| Лабораторная    | работа   | <b>№2.</b> | Мультиплексоры    | И  |

| демультиплексор | оы       |            |                   | 9  |

| Лабораторная ра | бота №3. | Суммато    | ры                | 13 |

| Лабораторная ра | бота №4. | Триггері   | ы                 | 17 |

| Лабораторная ра | бота №5. | Двоичнь    | ые счетчики       | 25 |

| список исполь   | ЗОВАННЫ  | х источ    | <b>-</b> НИКОВ    | 31 |

#### **ВВЕДЕНИЕ**

Схемотехника изучает основы построения аппаратных средств аналоговых и цифровых устройств. В данном курсе будут рассматриваться основы цифровой схемотехники.

Лабораторные работы направлены на изучение принципов действия комбинационных и накапливающих узлов цифровых устройств.

# ЛАБОРАТОРНАЯ РАБОТА №1. ДЕШИФРАТОРЫ И ШИФРАТОРЫ

**Цель работы** – Практическое изучение принципов действия дешифратора и шифратора.

#### Теоретические сведения

**Дешифратор** — это универсальный преобразователь, при помощи которого выполняется преобразование всех комбинаций значений п двоичных переменных в один из 2n выходных сигналов, то есть дешифратор — это операционный узел ЭВМ, выполняющий микрооперацию преобразования двоичного кода в условно-десятичный.

По способу реализации дешифраторы могут быть линейные, прямоугольные и пирамидальные.

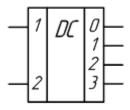

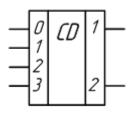

Рис. 1 – Пример двувходного дешифратора

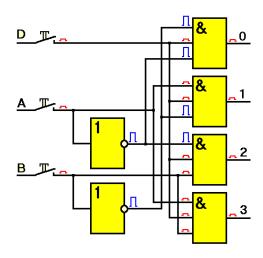

Рис. 2 – Схема дешифратора

Таблица 1 – Таблица истинности дешифратора

| x1 | x2 | y0 | y1 | y2 | у3 |

|----|----|----|----|----|----|

| 0  | 0  | 1  | 0  | 0  | 0  |

| 0  | 1  | 0  | 1  | 0  | 0  |

| 1  | 0  | 0  | 0  | 1  | 0  |

| 1  | 1  | 0  | 0  | 0  | 1  |

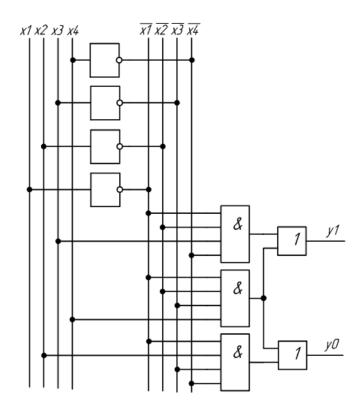

**Шифратор** выполняет функцию, обратную декодеру (дешифратору), то есть преобразует непозиционный (унитарный) двоичный 2n разрядный код 8n разрядный позиционный код. При подаче на один из входов единичного сигнала на выходе формируется соответствующий двоичный код. Составим таблицу истинности шифратора при n=2.

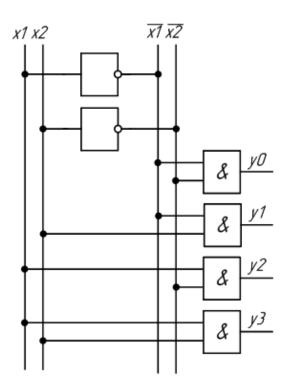

Рис. 4 – Пример шифратора

Рис. 5 – Схема шифратора

| Таблица 2 – Таблица истинности шифратор | Габлица : | а 2 – Таблица і | истинности | шифратора |

|-----------------------------------------|-----------|-----------------|------------|-----------|

|-----------------------------------------|-----------|-----------------|------------|-----------|

| x1 | x2 | x3 | x4 | y1 | y0 |

|----|----|----|----|----|----|

| 1  | 0  | 0  | 0  | 0  | 0  |

| 0  | 1  | 0  | 0  | 0  | 1  |

| 0  | 0  | 1  | 0  | 1  | 0  |

| 0  | 0  | 0  | 1  | 1  | 1  |

#### Задания

Преобразователи кодов наиболее известны в применение к цифровым индикаторам. Например, преобразователь 4-х разрядного позиционного двоичного кода в десятичные цифры. Имеется семи сегментный индикатор и с его помощью требуется высветить десять цифр.

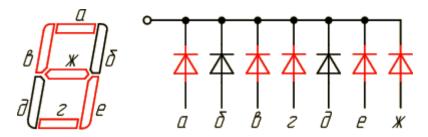

Рис. 7 – Семисегментный индикатор

Очевидно, что двоичный код должен иметь не менее 4 - x разрядов ( $2^4 = 16$ , что больше 10).

Составить таблицу истинности такого преобразователя.

Написать логические выражения для всех выходов.

Составить принципиальную схему и реализовать её в программе.

# ЛАБОРАТОРНАЯ РАБОТА №2. МУЛЬТИПЛЕКСОРЫ И ДЕМУЛЬТИПЛЕКСОРЫ

**Цель работы** – Практическое изучение принципов действия мультиплексора и демультиплексора.

**Мультиплексор (коммутатор)** — операционный узел ЭВМ, осуществляющий микрооперацию передачи сигнала с одного из своих информационных входов на один выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

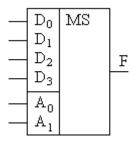

Рис. 1. – Принципиальное обозначение мультиплексора

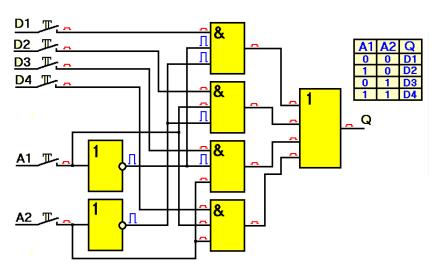

Рис. 2. – Логическая схема мультиплексора

Мультиплексор с приведенной функциональной схемой имеет 4 информационных входа, 2 управляющих входа и 1 выход. Поэтому он называется «1 из 4». Основное его предназначение - пересылка с определенного входа на выход. Выбор того входа, откуда пересылаются данные, определяется двоичным кодом, поступающим на управляющие (селекторные) входы. Для выбора номера входа, откуда необходимо взять данные, достаточно подать на входы А и В двоичный код, соответствующий нужному номеру. Например, подав на входы А и В код 11, зададим как бы подключение выхода ко входу №3.

Работу мультиплексора можно описать при помощи таблицы истинности.

Его схема представляет собой дешифратор с объединенными выходами. К каждому элементу И дешифратора (их число равно числу коммутируемых каналов) подводятся сигналы, соответствующие каналу и управляющему коду номера канала. Выходы всех элементов И объединяются элементом ИЛИ.

При работе коммутатора ни о каком физическом подключении одного из входов устройства к его выходу речи не идет. Сигнал на выходе коммутатора лишь ПОВТОРЯЕТ сигнал на входе с номером, заданным кодом на входах А и В. В этом и заключается отличие коммутатора электронного от механического.

В технике связи подобное устройство можно применить для приема сигналов от телефонных линий абонентов-источников и подключения одного из них к телефонному коммутатору — абонентов-источников несколько, телефонный коммутатор один).

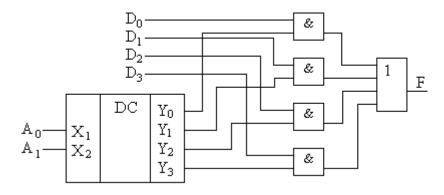

Рис. 3 – Реализация мультиплексора на базе дешифратора

**Демультиплексор** — это управляемый кодом узел цифровых устройств, предназначенный для передачи сигналов от одного физического канала на несколько выходных линий. Иначе — распределитель сигналов.

#### Работа демультиплексора

Работа его заключается в том, что на одном из выходов (на каком именно — определяет код на управляющих входах A и B) появляется такой же сигнал, как и на информационном входе D. Это же подтверждается и таблицей истинности.

Как и при работе коммутатора, при работе демультиплексора ни о каком физическом подключении его входа к одному из его выходов речи не идет. Сигнал на выходах демультиплексора (номер выхода определяет код на входах А и В) лишь ПОВТОРЯЕТ сигнал на его входе D. В этом и заключается отличие распределителя сигналов электронного от механического.

В технике связи можно было применить подобное устройство для подключения телефонным коммутатором определенного абонента-источника к линии другого абонента — абонента-адресата: коммутатор один — абонентов-адресатов несколько.

| Α |   |   |   |   |   |

|---|---|---|---|---|---|

| ^ | В | 0 | 1 | 2 | 3 |

| 0 | 0 | ם | 0 | 0 | 0 |

| 1 | 0 | 0 | D | 0 | 0 |

| 0 | 1 | 0 | 0 | D | 0 |

| 1 | 1 | 0 | 0 | 0 | D |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

|   |   |   |   |   |   |

Рис. 4 – Схема демультиплексора

#### Задания

- 1. Ознакомиться с назначением мультиплексора и демультиплексора.

- 2. Разработать схему мультиплексора на шесть 11

# Управление дистанционного обучения и повышения квалификации

#### Схемотехническое проектирование средств ВТ

информационных входа и демультиплексора на шесть информационных выхода объединенных единым каналом.

- 3. Описать назначение элементов входящих в схему.

- 4. Создать таблицы истинности для мультиплексора и демультиплексора.

- 5. Описать работу схемы разработанного устройства.

- 6. Подготовиться к защите лабораторной работы

#### ЛАБОРАТОРНАЯ РАБОТА №3. СУММАТОРЫ

**Цель работы** — Практическое изучение логических элементов, реализующих элементарные функции алгебры логики (ФАЛ). Экспериментальное исследование логических элементов в программе qucs.

#### Теоретические сведения

**Сумматор** – операционный узел ЭВМ, выполняющий арифметическое суммирование кодов чисел. Сумматор является одним из основных узлов АЛУ.

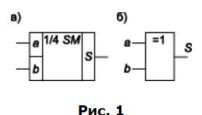

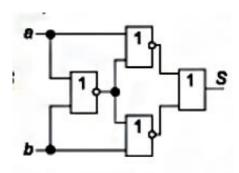

#### Четвертьсумматор

Простейшим двоичным суммирующим элементом является четвертьсумматор. Происхождение названия этого элемента следует из того, что он имеет в два раза меньше выходов и в два раза меньше строк в таблице истинности по сравнению с полным двоичным одноразрядным сумматором. Наиболее известны для данной схемы названия: элемент "сумма по модулю 2" и элемент "исключающее ИЛИ". Схема (рис. 1) имеет два входа а и в для двух слагаемых и один выход S для суммы. Работу ее отражает таблица истинности 1 (табл. 1), а соответствующее уравнение имеет вид:

$$S = \bar{a}b + a\bar{b} = a \oplus b$$

Таблица 1

| a | b | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Рис. 2 – Схема на базе логических элементов

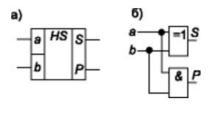

**Полусумматор** (рис. 3) имеет два входа a и b для двух слагаемых и два выхода: S сумма, P перенос. Обозначением полусумматора служат буквы HS (halfsum — полусумма). Работу его отражает таблица истинности (табл. 2), а соответствующие уравнения имеют вид:

$$S=\bar{a}b+a\bar{b}=a\oplus b$$

## Таблица 2

Рис. 3

| a b P S |  |

|---------|--|

| 0000    |  |

| 0 1 0 1 |  |

| 1001    |  |

| 1 1 1 0 |  |

Из уравнений (5) следует, что для реализации полусумма-14

тора требуется один элемент "исключающее ИЛИ" и один двух-входовый вентиль И (рис. 36).

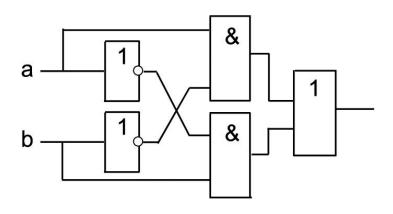

**Полный сумматор** — это устройство для сложения трех одноразрядных чисел. Такая задача возникает при сложении двух многоразрядных чисел, когда в качестве третьего слагаемого учитывается перенос от сложения предыдущих разрядов.

$$_{P=\bar{a}bp+a\bar{b}p+ab\bar{p}+abp}^{S=\bar{a}\bar{b}p+\bar{a}b\bar{p}+abp} \}$$

Таблица 3

Рис. 4

| ≟ наб. | a | b | р | P | S |

|--------|---|---|---|---|---|

| 0      | 0 | 0 | 0 | 0 | 0 |

| 1      | 0 | 0 | 1 | 0 | 1 |

| 2      | 0 | 1 | 0 | 0 | 1 |

| 3      | 0 | 1 | 1 | 1 | 0 |

| 4      | 1 | 0 | 0 | 0 | 1 |

| 5      | 1 | 0 | 1 | 1 | 0 |

| 6      | 1 | 1 | 0 | 1 | 0 |

| 7      | 1 | 1 | 1 | 1 | 1 |

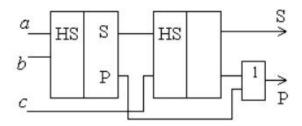

Полный сумматор строится на базе двух полусумматоров (рис.5).

Рис. 5 – Схема полного сумматора на базе двух полусумматоров

Используя полный сумматор, можно построить суммирующее устройство для сложения многоразрядных двоичных чисел.

#### Задания

1. Реализовать схему четвертьсумматора в базисе элементаИ-НЕ по уравнению:

$$S = \bar{a}b + a\bar{b} = \bar{a}a + \bar{a}b + \bar{b}b + a\bar{b} = \underline{a}\bar{a}b + b\bar{a}\bar{b} = a\bar{a}\bar{b} \cdot b\bar{a}\bar{b}$$

$$= a(\bar{a} + \bar{b}) + b(\bar{a} + \bar{b}) = a\bar{a}\bar{b} + b\bar{a}\bar{b} = a\bar{a}\bar{b} \cdot b\bar{a}\bar{b}$$

2. Получить логическое выражение четвертьсумматорав базисе приведенной схемы. Показать вывод полученного выражения с помощью законов алгебры Буля (подобно примеру в задании 1).

- 3. Черными точками на схеме обозначены места разветвления проводников.

- 4. Реализовать схему полусумматора в базисе логических элементов ИЛИ-НЕ.

- 5. Реализовать схему полного сумматора в базисе логических элементов И-НЕ.

#### **ЛАБОРАТОРНАЯ РАБОТА №4. ТРИГГЕРЫ**

**Целью** работы является экспериментальное исследование работы различных типов триггеров.

**Триггер** – это переключающее устройство, имеющее два устойчивых состояния – нуля или единицы.

Триггеры используются для построения временных логических схем. На базе триггеров строят схемы счётчиков и регистров. Рассмотрим логику работы следующих типов триггеров:

- 1) RS-триггер (управляемый нулем, управляемый единицей);

- 2) синхронный RS-триггер;

- 3) МS-триггер (двухступенчатый);

- 4) Т-триггер (синхронный, асинхронный);

- 5) D-триггер;

- 6) ЈК-триггер.

#### Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений). Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

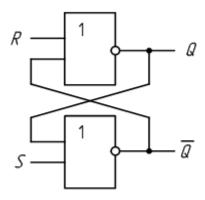

#### RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер.

RS-триггер имеет два логических входа:

- R установка 0 (от слова reset);

- S установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q прямой;

- Q обратный (инверсный).

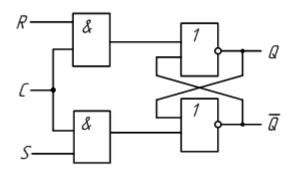

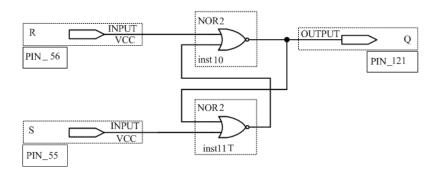

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью (рис.1).

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль — со входа R, другой — с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента. Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в "0". Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния.

Рис. 1 – Схема простейшего RS- триггера

Для описания работы триггера используют таблицу состояний (переходов).

#### Обозначим:

- Q(t) состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- ullet Q(t+1) состояние триггера после изменения на входах R и S.

Таблица 1. Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения            |

|---|---|------|--------|----------------------|

| 0 | 0 | 0    | 0      | Режим хранения       |

| 0 | 0 | 1    | 1      | информации R=S=0     |

| 0 | 1 | 0    | 1      | Режим установки      |

| 0 | 1 | 1    | 1      | единицы S=1          |

| 1 | 0 | 0    | 0      | Режим установки нуля |

| 1 | 0 | 1    | 0      | R=1                  |

| 1 | 1 | 0    | *      | R=S=1 запрещённая    |

| 1 | 1 | 1    | *      | комбинация           |

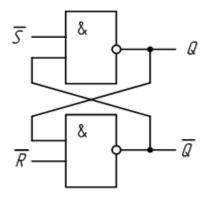

RS-триггер можно построить и на элементах "И-НЕ" (рис. 2).

Рис.2 – Схема RS-триггера, построенного на схемах "2И-НЕ"

Входы R и S инверсные (активный уровень "0"). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов "0". Комбинация R=S=0 является запрещённой.

Таблица 2. Таблица переходов RS триггера в базисе "2И-НЕ"

| R | S | Q(t) | Q(t+1) | Пояснения         |

|---|---|------|--------|-------------------|

| 0 | 0 | 0    | *      | R=S=0 запрещённая |

| 0 | 0 | 1    | *      | комбинация        |

| 0 | 1 | 0    | 0      | Режим установки   |

| 0 | 1 | 1    | 0      | нуля R=0          |

| 1 | 0 | 0    | 1      | Режим установки   |

| 1 | 0 | 1    | 1      | единицыS=0        |

| 1 | 1 | 0    | 0      | Режим хранения    |

| 1 | 1 | 1    | 1      | информации R=S=1  |

#### Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется "опасные гонки"), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена на рисунке 3.

Рис.3 – Схема синхронного RS-триггера

| R | S | С | Q(t) | Q(t+1) | Пояснения               |

|---|---|---|------|--------|-------------------------|

| 0 | 0 | 1 | 0    | 0      | Режим хранения          |

| 0 | 0 | 1 | 1    | 1      | информации<br>R = S = 0 |

| 0 | 1 | 1 | 0    | 1      | Режим установки         |

| 0 | 1 | 1 | 1    | 1      | единицы S =1            |

| 1 | 0 | 1 | 0    | 0      | Режим установки нуля    |

n

Таблица 3. Таблица переходов синхронного RS-триггера

R=1

R = S = 1 запрещённая

комбинация

В таблице 3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

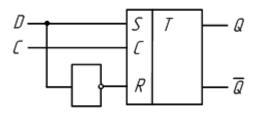

#### **D** – триггер

0

1

1

1

1

1

1

0

1

1

1

1

D-триггер имеет 1 информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход C).

Рис.4 – Схема D-триггера на основе синхронного RS-триггера

Таблица 4. Таблица переходов D-триггера

| С | D | Q(t) | Q(t+1) | Пояснения      |

|---|---|------|--------|----------------|

| 0 | * | 0    | 0      | Режим хранения |

| 0 | * | 1    | 1      | информации     |

| 1 | 0 | *    | 0      | Режим записи   |

| 1 | 1 | *    | 1      | информации     |

Если на входе D — "1", то по приходу синхроимпульса Q = 1. Если на D "0", то Q =0.

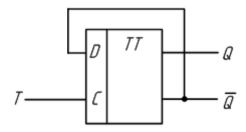

#### Счётный триггер (Т-триггер)

Т-триггер имеет один счётный информационный вход. Триггер переключается каждый раз в противоположное состояние, когда на вход Т поступает управляющий сигнал.

Таблица 5. Таблица переходов Т триггера

| Т | Q(t) | Q(t+1) |

|---|------|--------|

| 0 | 0    | 0      |

| 0 | 1    | 1      |

| 1 | 0    | 1      |

| 1 | 1    | 0      |

Рис.5 – Схема Т-триггера на основе двухступенчатого D-триггера

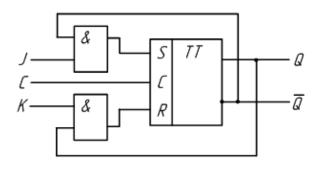

#### Универсальный триггер (ЈК-триггер)

Такой триггер имеет информационные входы J и K, которые по своему влиянию аналогичны входам S и R тактируемого RS-триггера:

- 1. при J=1, K=0 триггер по тактовому импульсу устанавливается в состояние Q=1;

- 2. при J = 0, K = 1 переключается в состояние <math>Q = 0;

- 3. при J=K=0 хранит ранее принятую информацию.

Но в отличие от синхронного RS-триггера одновременное присутствие логических 1 на информационных входах не является для JK-триггера запрещённой комбинацией и приводит триггер в противоположное состояние.

Рис.6 – Схема ЈК-триггера на основе двухступенчатого синхронного RS-триггера.

C Q(t) Q(t+1) K

Таблица 6. Таблица переходов ЈК триггера

# Задания

- 1. Исследовать асинхронный RS- триггер

- 2. Сконфигурировать ПЛИС в соответствии с рисунком 7.

Рис.7 – RS-триггер на основе логических элементов "ИЛИ-НЕ"

3. Устанавливая с помощью переключателей S7 и S8 различные комбинации логических уровней и наблюдая за светодиодом LED8 заполнить таблицу 7.

Таблица 7. Таблица переходов для асинхронного RS триггера на элементах "ИЛИ-НЕ"

| R | S | Q(t) | Q(t+1) |

|---|---|------|--------|

| 0 | 0 | 0    |        |

| 0 | 0 | 1    |        |

| 0 | 1 | 0    |        |

| 0 | 1 | 1    |        |

| 1 | 0 | 0    |        |

| 1 | 0 | 1    |        |

#### Контрольные вопросы

- 1. Чем определяется быстродействие триггера?

- 2. Начертить схему RS-триггера на логических элементах "ИЛИ-НЕ" и пояснить принцип его работы.

- 3. Почему ЈК-триггер называется универсальным?

- 4. Пояснить по таблице переходов работу D-триггера.

- 5. Какой характерной особенностью обладает периодическая последовательность импульсов на входе Т-триггера?

- 6. Способы описания последовательных цифровых устройств.

- 7. Каким преимуществом обладает двухступенчатый триггер?

# ЛАБОРАТОРНАЯ РАБОТА №5. ДВОИЧНЫЕ СЧЕТЧИКИ

**Целью** работы является изучение универсального двоичного счётчика

**Счётчик** — это цифровая схема, которая под действием входных импульсов переходит из одного состояния в другое, фиксируя тем самым число поступивших на её вход импульсов в том или ином коде.

Основной операцией счётчиков является изменение содержимого счётчика на единицу ( иногда условную). Если единица прибавляется, то счётчик называется суммирующим и выполняет операцию инкрементации. Если счётчик единицу вычитает, то он называется вычитающим и выполняет операцию декрементации. Если счётчик и суммирует, и вычитает, то он называется реверсивным.

Главная характеристика счётчика-модуль (коэффициент пересчёта). Модуль определяет максимальное число возможных состояний счётчика.

В основном счётчики строятся на триггерах типа JK и типа T.

#### Параметры счётчика:

- модуль счёта М число устойчивых состояний;

- ёмкость E максимальное число, которое может быть записано в счётчик (E=M-1);

- быстродействие (скорость перехода из состояния «все 1» в состояние «все 0» и наоборот).

#### Классификация счетчиков:

- 1. По направлению счёта:

- суммирующие;

- вычитающие;

- реверсивные;

- 2. По способу построения цепи переноса:

- с последовательным переносом;

- с параллельным переносом;

- с комбинированным переносом;

- 3. По способу переключения триггера:

- синхронные;

- асинхронные.

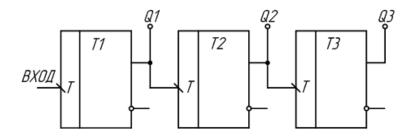

#### Простейший суммирующий асинхронный счётчик

Счётчик представляет собой несколько последовательно включенных счётных триггеров. Напомним, что по каждому входному импульсу счётный триггер изменяет своё состояние на противоположное.

Рис.1 – Простейший суммирующий асинхронный счётчик

Если вход синхроимпульса триггера отмечен как «\», то опрокидывание триггера происходит по заднему фронту, если как «/» — то по переднему.

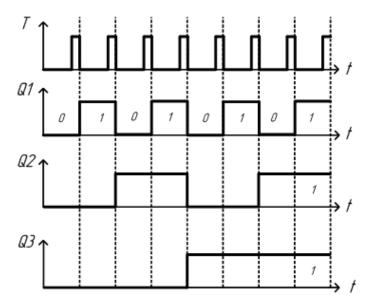

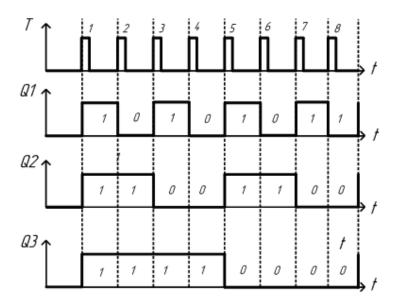

Рис.2 – Временная диаграмма работы суммирующего асинхронного счётчика

Для того чтобы разобраться, как работает схема двоичного счётчика, воспользуемся временными диаграммами сигналов на входе и выходах этой схемы, приведёнными на рисунке 2.

Пусть первоначальное состояние всех триггеров счётчика будет нулевым. Это состояние мы видим на временных диаграммах. Запишем его в таблицу 1. После поступления на вход счётчика тактового импульса (который воспринимается по заднему фронту) первый триггер изменяет своё состояние на противоположное, то есть единицу.

Запишем новое состояние выходов счётчика в ту же самую таблицу. Так как по приходу первого импульса изменилось состояние первого триггера, то этот триггер содержит младший разряд двоичного числа (единицы).

Таблица 2.1 – Изменение уровней на выходе суммирующего двоичного счётчика при поступлении на его вход импульсов

| Номер входного импульса | Q2 | Q1 | Q0 |

|-------------------------|----|----|----|

| 1                       | 0  | 0  | 1  |

| 2                       | 0  | 1  | 0  |

| 3                       | 0  | 1  | 1  |

| 4                       | 1  | 0  | 0  |

| 5                       | 1  | 0  | 1  |

| 6                       | 1  | 1  | 0  |

| 7                       | 1  | 1  | 1  |

| 8                       | 0  | 0  | 0  |

Подадим на вход счётчика ещё один тактовый импульс. Значение первого триггера снова изменится на прямо противоположное. На этот раз на выходе первого триггера, а значит и на входе второго триггера сформируется задний фронт. Это означает, что второй триггер тоже изменит своё состояние на противоположное. Это отчётливо видно на временных диаграммах, приведённых на рисунке 2. Запишем новое состояние выходов счётчика в таблицу 1. В этой строке таблицы образовалось двоичное число 2. Оно совпадает с номером входного импульса.

Продолжая анализировать временную диаграмму, можно определить, что на выходах приведённой схемы счётчика последовательно появляются цифры от 0 до 7. Эти цифры записаны в двоичном виде. При поступлении на счётный вход счётчика очередного импульса, содержимое его триггеров увеличивается на 1. Поэтому такие счётчики получили название суммирующих двоич-

ных счётчиков. Если информацию снимать с инверсных выходов триггеров, то получится вычитающий счётчик.

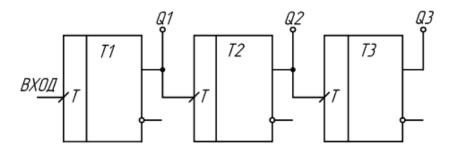

#### Простейший вычитающий асинхронный счётчик

Рассмотрим схему счётчика на триггерах, опрокидывающихся по переднему фронту входных импульсов (рис.3).

Из временной диаграммы видим, что получился вычитающий счётчик. Если информацию снимать с инверсных выходов триггеров, то получится суммирующий счётчик.

Рис.3 – Вычитающий счётчик

Рис. 4 – Временная диаграмма

#### Счётчик с произвольным модулем счёта

Для построения такого счётчика можно использовать двоичный счётчик, у которого модуль счёта М должен быть больше модуля счёта разрабатываемого счётчика с произвольным модулем счёта.

Пусть нужно сделать счётчик с М= 10.

У 4-х разрядного счётчика модуль счёта равен 16 (больше 10).

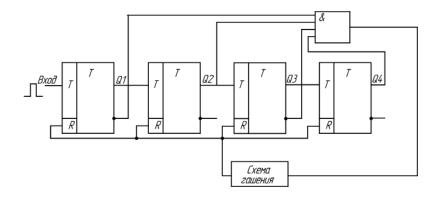

Схема счётчика представляет собой 4 последовательно включённых счётных триггера, у которых есть вход сброса R.

Число 10 в двоичной системе счисления представляется 1010. Когда на выходах счетчика будет код 1010, на выходе элемента «И» появится логическая единица, которая запустит схему гашения. Длительность импульса на выходе схемы гашения должна быть достаточна для надёжного сброса всех триггеров счётчика в 0. Разряды числа 1010, равные 1 подаются на схему «И» с прямых выходов триггеров, а равные 0-c инверсных. Таким образом, как только счётчик досчитает до 10, произойдёт обнуление всех триггеров и счёт продолжится с кода 0000.

Рис.5 – Счётчик с модулем счета М=10

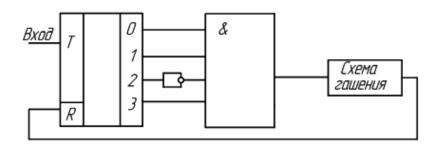

Рассмотрим счётчик с M=11 на основе двоичного счётчика в одной микросхеме (без инверсных выходов).

1110=10112

Рис.6 – Счётчик с модулем счёта М=11

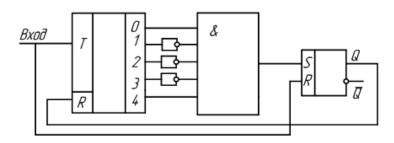

В качестве схемы гашения может быть RS-триггер.

Рис.7 – Счётчик с модулем счёта М=17

В этой схеме  $M=10001_2=17_{10}$

Сигнал на входе К счётчика будет действовать в течение одного периода входных импульсов

#### Задание

Построить суммирующий счётчик в программе.

#### Контрольные вопросы

- 1. Объяснить принцип работы суммирующего счётчика.

- 2. Изобразить временные диаграммы работы суммирующего счётчика.

- 3. Объяснить принцип работы вычитающего счётчика.

- 4. Изобразить временные диаграммы работы вычитающего счётчика.

- 5. Объяснить принцип работы счётчика с произвольным модулем счёта.

- 6. Рассказать о классификации счётчиков.

- 7. Где применяются счётчики?

#### СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

- 1. Базарова И.А. Цифровая схемотехника Ухта: УГТУ, 2004. 134 с.

- 2. Потехин В.А. Схемотехника цифровых устройств: учеб. пособие для вузов Томск: В-Спектр, 2012. 250с.

- 3. В.А. Алехин. Электроника и схемотехника М.: МИРЭА, 2016. 337 с.